## A Review on Design of Sub Threshold Inverter

Sindhu R<sup>1</sup>, Shilpa Mehta<sup>2</sup>

<sup>1</sup>Assistant Professor, Department of E&CE, Proudhadevaraya Institute of Technology, Hospet, Karnataka <sup>2</sup>Professor & HOD, Department of E&CE, Presidency University, Bangalore, Karnataka

**Abstract:** The prediction of Gordon Moore has directed the innovation in integrating more and more devices on a single chip resulted in million devices integrating on a chip. Power consumption and dissipation or generation of more heat has brought a limit to the integration of more transistors. Design of a transistor working in sub threshold region where conduction is done due to minority charge carriers is a solution to decrease the consumption of power. **Key words:** CMOS, Process voltage, Sub threshold voltage, Threshold voltage.

#### 1. Introduction

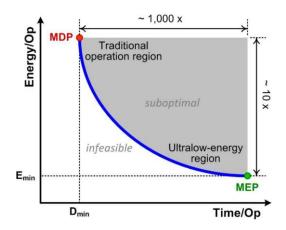

In the fabrication of transistors the concept of scaling of devices was used where length and width of channel was scaled oxide thickness and power supply was also scaled. Since the channel length between source and drain was getting reduced the concept moved to make the transistor work in a condition where the supply voltage is less than threshold voltage and minority carriers are used for conductions.[3]

The concept of making the transistor work in sub threshold are ideal for applications where performance is not important and the main criteria is reducing energy consumption. Low performance is due to instability increased variations and functional failure.[5]

Management of power allowed the exploration of sub threshold circuit operation. Intention for low power design is aimed in decreasing the power dissipation in the surroundings. The demand for energy consumption has drastically increased since every electronic goods have become part and parcel of common man. The fabrication cost is decreased due to less power consumption and less heat generation. The behavior of sub threshold circuits is affected by voltage and temperature variations. [2]

### 2. Working of inverter.

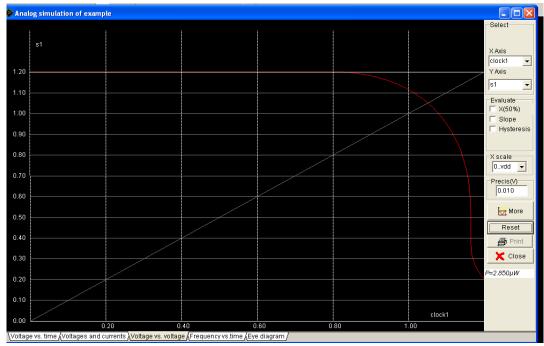

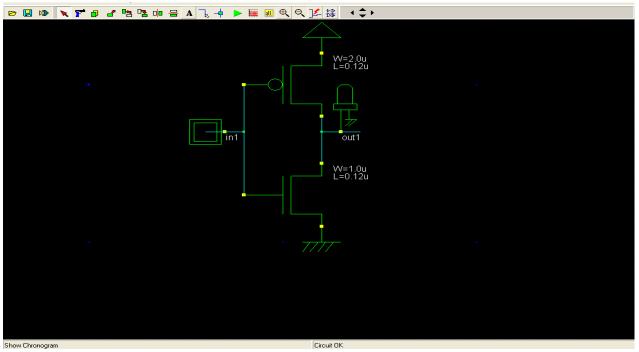

In all digital circuits inverter is the basic block. The supply voltage for inverter is decreased and made less than threshold voltage. The transfer characteristic is shown in below simulation graph. A CMOS inverter is designed using pmos and nmos where the inverter works as follows i.e. when input is high nmos starts conduction and when input is low pmos starts conduction.[1]

Figure 1 Transfer characteristics of inverter.

Figure 2 Schematic diagram of inverter.

# International Journal of Electronics Engineering (ISSN: 0973-7383) Volume 10 • Issue 2 pp. 413-415 June 2018-Dec 2018 www.csjournals.com

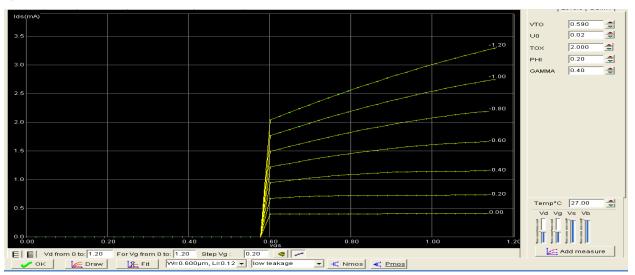

Figure 3 Variations of drain and gate voltages

### **Conclusions**

Management of power allowed the exploration of sub threshold circuit operation. Design of a transistor working in sub threshold region is a solution to decrease the consumption of power. Basis for low power design is related to decrease the power dissipation to the surroundings. An optimization path can be taken between speed and power consumption for certain application. An effort is made to design an inverter which satisfies the condition.

### References

- [1] Srinivasa Rao.Ijjada, S.V.Sunil Kumar, M. Dinesh Reddy, Sk Abdul Rahaman, Dr.V malleswara Rao "Design of low power and high speed inverter" (IJDPS) Vol2, No 5, September 2011.

- [2] Wang, Alice, Benton H. Calhoun and Anantha P Chandrakasan. Sub threshold design for ultra low power systems, Springer

- [3] A.P.Chandrakasan, S.Sheng, R.W,Brodersen"low power CMOS Digital design", ], IEEE journal of solidstate circuits, pp. 473, vol 27, no 4, april 1992.

- [4] Kursen V Friedman EBMulti-voltage CMOS circuit design. John Wiley & Sons Ltd 2006.

- [5] Sherif M Sharroush Analysis of the subthreshold CMOS logic inverterAin Shams Eng J(2016)

- [6] Wolf W. Modern VLSI design: IP-based design. 4th ed. PrenticeHall; 2009.

- [7] Meek LAP, Schneider MC, Galup-Montoro C. Ultra-low voltage CMOS logic circuits. In: Argentine conference on micronanoelectronics, echnology, and applications (EAMTA), 24–25 Jul., Mendoza; 2014. p. 1–7.

- [8] Soeleman H, Roy K. Digital CMOS logic operation in the subthreshold region. In: Proceedings of the 10th great lakes symposium on VLSI, New York, NY, USA; 2000. p. 107–12.

- [9] Srinivasa Rao. Ijjada, S.V. Sunil Kumar, M. Dinesh Reddy, Sk. Abdul Rahaman, Dr. V. Malleswara Rao, "Design of low power and high speed inverter," International Journal of Distributed and Parallel Systems (IJDPS) Vol. 2, No. 5, September 2011.

- [10] Hendrawan Soeleman and Kaushik Roy, "Ultra-Low Power Digital Subthreshold Logic Circuits," International Journal of Distributed and Parallel Systems (IJDPS) Vol.2, No.5, September 2011.

- [11] Vishal Sharma, Sanjay Kumar, "Design of Low-Power CMOS Cell Structures Using Sub threshold Conduction Region," International Journal of Scientific & Engineering Research, Volume 2, Issue 2, February 2011