# Design & Analysis of Two Stage CMOS Operational Amplifier for Low Power Design

<sup>1</sup>Lakshya Miglani, <sup>2</sup>Sanjeev Dhull, <sup>3</sup>Ramnish Kumar <sup>1</sup>M.Tech. Student, <sup>2</sup>Professor, <sup>3</sup>Associate Professor Department of Electronics & Communication Engineering Guru Jambheshwar University of Science & Technology, Hisar-125001, Haryana, India

**Abstract:** Operational amplifiers are widely used and versatile electronics device and in this proposed work a two stage OpAmp is simulated utilizing 90nm technology on an EDA tool called Cadence Virtuoso. The purpose of purposed work is to develop a 2-stage CMOS OpAmp for low power with greater stability and to examine how different components affect its design characteristics. Voltage Gain for amplification, Phase Margin for stability, Unity Gain Frequency and Power Dissipation are the primary parameters that proposed amplifier aims to improve. A differential amplifier with a current mirror active load and a common-source amplifier make up the two stages of OpAmp.

Keyword: 2-stage CMOS operational amplifier, gain, unity gain frequency, phase margin and power dissipation.

## **1. INTRODUCTION**

Fundamentally, an amplifier is a device that increases input signal strength and is intended to be operated in combination with external feedback elements between its output and input terminals, such as resistors and capacitors [1]. The general term "amplifier" is used to describe a circuit that produces a more powerful version of its input signal. Due to its capacity to amplify a relatively weak input signal, small signal amplifiers are frequently used devices. The operational amplifier studied, often known as an OpAmp, is a high-gain electronic voltage amplifier with differential input and that mostly has a single-ended output. The main goal of operational amplifier is to provide better amplification along with less power dissipation with higher bandwidth and greater phase margin for stability of amplifier [2-6]. With the right choice of the components and their values, the OpAmp can be used as a current to voltage converter, active rectifier, integrator, comparators, voltage follower, Differentiators, summing amplifier. Ideally an OpAmp should have infinite input resistance, infinity voltage gain, and zero output resistance [7]. However, after simulation the practical values will be discussed.

Figure 1: Symbol of OpAmp.

As shown in figure 1, an op-amp contains five terminals: inverting input, the output, non-inverting input, negative power supply (VSS or often grounded) and positive power supply (VDD). One of the inputs is Inverting Input and it is recognized by a "minus" (–) sign. The other input named as the Non-inverting Input and is indicated by a "plus" sign (+). The third terminal of OpAmp is its output terminal and it can be a current or voltage [8].

## 2. DESIGN PROCEDURE

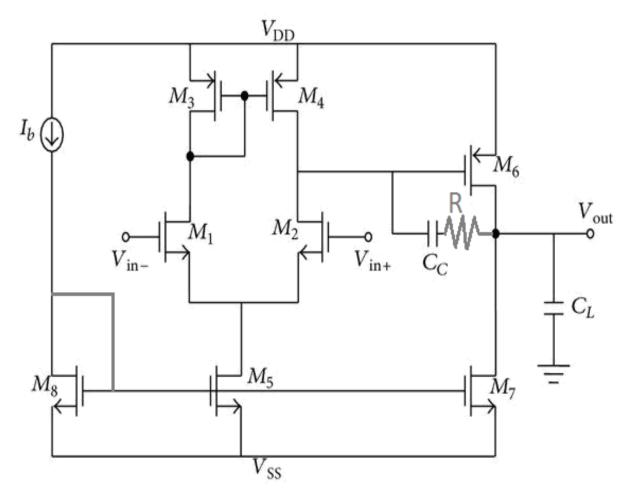

The 2-stage CMOS operational amplifier shown in figure 2 consists of two stages one is Differential-input singleended output stage with PMOS current mirror as active load, the differential amplifier have two inputs that is  $V_{in+}$ and  $V_{in-}$  as first stage and second one is a common-source amplifier output stage to provide more voltage gain because gain provided by first stage is not sufficient and to provide low output resistance common-source amplifier is used.

The schematic of two-stage operational amplifier design as shown in figure 2 contains of a NMOS differential amplifier (MOSFET  $M_1$  and  $M_2$ ) with active load PMOS current mirror (MOSFET  $M_3$  and  $M_4$ ) as the first stage next comes the second stage, which is made up of PMOS (MOSFET  $M_6$ ) and is common-source amplifier where mosfet  $M_6$  works as an amplifier and mosfet  $M_7$  works as the current source for biasing. Mosfet  $M_5$  and  $M_8$  form a NMOS current mirror and are used to bias the circuit to provide proper current and voltages to the circuit.

Figure 2: Two stage CMOS operational amplifier circuit diagram.

A feedback capacitor Cc that is connected between the second stage amplifier's input (or called as the first stage amplifier's output) and the second stage amplifier's output is used as a miller capacitance to obtain pole splitting (increasing the distance between the first and second pole) and that will provide better stability, along with capacitor Cc a resistor R that is called as nulling resistor and is connected to provide greater phase margin to achieve greater stability.

With the nulling resistor, we can move the RHP (right half plane) zero to infinity and a second option to achieve greater stability is to select R in a way that shifts RHP zero into the LHP (left half plane) such that it can be cancelled with one of the poles. However in this simulation we have chosen resistor R such that the RHP zero moves towards infinity or practically we can say towards a very higher frequency.

To achieve enhanced performance the values given to all the components of op-amp should be precise in a way that amplifier can achieve better gain, unity gain frequency, power dissipation and phase margin.

| Components          | Values                   |

|---------------------|--------------------------|

| V <sub>DD</sub>     | 1.2 V                    |

| R                   | 3.4 kΩ                   |

| C <sub>C</sub>      | 4.5 pF                   |

| CL                  | 10 pF                    |

| $\mathbf{V_{in}}^+$ | DC= 1 Volt : AC= -1 Volt |

| Vin                 | DC= 1 Volt : AC= 1 Volt  |

| V <sub>SS</sub>     | 0 Volt                   |

#### Table 1: Different components and their values.

# Table 2: Width and Length of all the MOSFET

| Mosfet's                        | Practical values (W) | Practical values (L) |

|---------------------------------|----------------------|----------------------|

| $M_1, M_2$                      | 11µ                  | 1μ                   |

| M <sub>3</sub> , M <sub>4</sub> | 10µ                  | 1μ                   |

| M <sub>5</sub> . M <sub>8</sub> | 8μ                   | 1μ                   |

| $M_6$                           | 50μ                  | 1μ                   |

| M <sub>7</sub>                  | 20µ                  | 1μ                   |

The width (W) and length (L) of all the mosfet's are described in table 2. Width and Length of mosfet is an important component of mosfet as by selecting the values of W and L in such a way that we can achieve greater gain, bandwidth and phase margin. The total width of mosfet  $M_3$  and  $M_4$  is 10 $\mu$  (WP=10  $\mu$ ) but the fingers for these mosfet are 5. Similarly total width of mosfet  $M_6$  is 50 $\mu$  (WPS=50  $\mu$ ) but the fingers for this mosfet are 2.

# 3. SIMULATION OF PROPOSED DESIGN

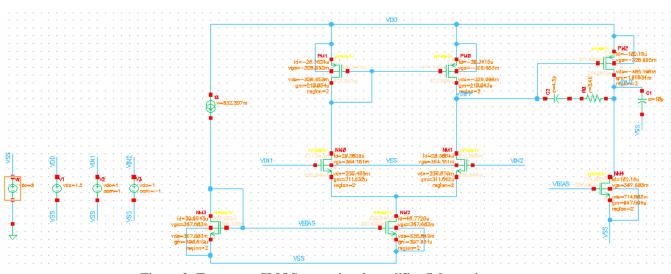

Make the connections as shown in the figure 3. Insert the values of components and mosfet parameters (W and L) as described in table 1 and 2 respectively. The two-stage operational amplifier used a compensation technique called as Miller compensation.

Prior to the unity gain frequency, the system behaved like a single pole system. OpAmp's are stabilized using this compensation method by connecting a capacitance Cc and resistor R in a negative-feedback configuration across one of the internal gain stages, usually the second stage.

Figure 3: Two-stage CMOS operational amplifier Schematic.

## 4. Results and Discussion

The results of AC and DC simulations and a discussion for the suggested two-stage operational amplifier are presented in this section. With 90nm technology, the OpAmp is simulated and examined using the cadence virtuoso EDA tool. A broad range of frequencies were covered. The gain of the OpAmp is not constant in the open loop design and fluctuates with frequency. The product of gain and frequency remains constant up until the gain bandwidth product of the OpAmp.

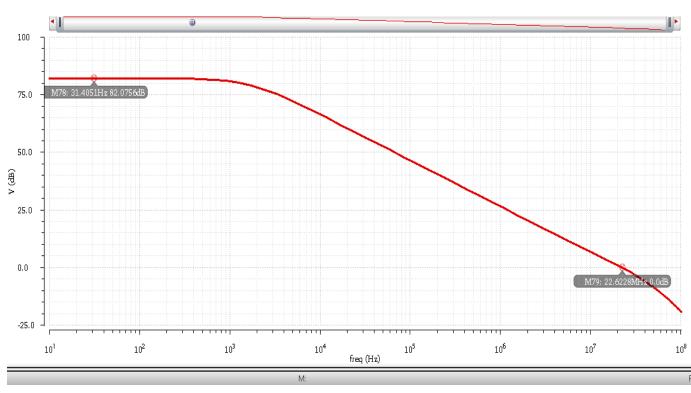

#### Figure 4: Gain in dB vs Frequency plot.

As shown in Figure 4, the graph of gain in dB vs frequency represents that the gain is of 82 dB at M78 mark and the unity gain frequency at 0dB is 22.6228 MHz at M79 mark. The unity gain frequency is also called as gain bandwidth product. The proposed result of gain is greater than 82% than the previous result [15].

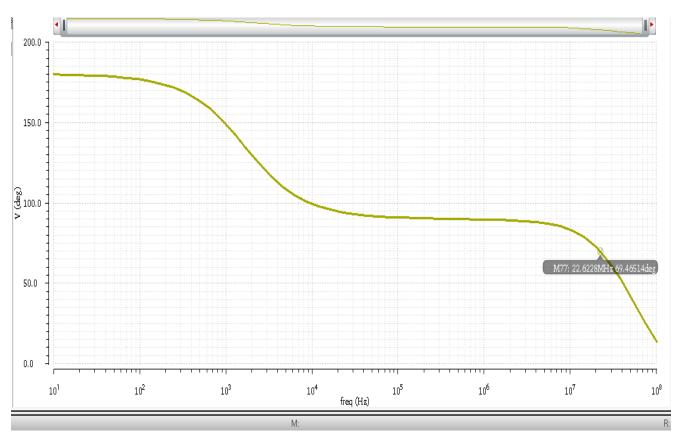

As shown in Figure 5, the graph represents that the phase margin at mark M77 where the gain bandwidth product is 22.6228 Mhz comes to be  $69^{\circ}$  that is remarkable for a 2-stage CMOS OpAmp to be stable. The previous result for phase margin was  $60^{\circ}$  and now it is  $69^{\circ}$  which is increased by  $9^{\circ}$ , which is an increment of 15% from the previous value [15].

The power dissipation is the total amount of power that is consumed by the circuit. The power dissipation comes to be  $219.6\mu$ W as shown in figure 6 which is quite low from previous result. The previous result of the parameter power dissipation was  $271\mu$ W which is greater than the present result. The power dissipation is reduced by 19% from the previous result [15].

Figure 5: Phase vs Frequency Plot.

| Detail | <u> </u>              |                  | 🚄 Replace | . 🕅 🔽          | <u>il</u> [ | 🖌 💌 🏹          | , |                | 0 4 | 2              |   |                |     |

|--------|-----------------------|------------------|-----------|----------------|-------------|----------------|---|----------------|-----|----------------|---|----------------|-----|

|        | Test                  | Output           | Nominal   | Spec   Weig    | ht   Pass   | /Fail          |   |                |     |                |   |                |     |

| mos_c  | char2_1:schematic_N:1 | Power Dissipatio | on 219.6u |                |             |                |   |                |     |                |   |                |     |

|        |                       |                  |           |                |             |                |   |                |     |                |   |                |     |

|        |                       |                  |           |                |             |                |   |                |     |                |   |                |     |

|        |                       |                  |           |                |             |                |   |                |     |                |   |                |     |

|        |                       |                  |           |                |             |                |   |                |     |                |   |                |     |

|        |                       |                  |           |                |             |                |   |                |     |                |   |                |     |

|        |                       |                  |           |                |             |                |   |                |     |                |   |                |     |

|        |                       |                  |           |                |             |                |   |                |     |                |   |                |     |

|        |                       |                  |           |                |             |                |   |                |     |                |   |                |     |

|        |                       |                  |           |                |             |                |   |                |     |                |   |                |     |

|        |                       |                  |           |                |             |                |   |                |     |                |   |                |     |

|        |                       |                  |           |                |             |                |   |                |     |                |   |                |     |

|        |                       |                  |           |                |             |                |   |                |     |                |   |                |     |

| ve.62  | D Interactive.63      | 🛛 🕗 Interactiv   | re.64 🚺 🕗 | Interactive.65 | 0           | Interactive.66 | 0 | Interactive.67 | 0   | Interactive.68 | 0 | Interactive.69 | • • |

|        |                       |                  |           |                |             |                |   |                |     |                |   | interactive.00 |     |

|        |                       |                  |           | M:             | _           |                | _ |                | _   |                | _ |                |     |

# Figure 6: Power Dissipation Calculation.

| Parameters              | Previous<br>Results[15] | T T T T  |                      |  |  |

|-------------------------|-------------------------|----------|----------------------|--|--|

| Gain                    | 45 dB                   | 82 dB    | Increased by 82%     |  |  |

| Phase Margin            | $60^{\circ}$            | 69°      | Increased by 15%     |  |  |

| Power Dissipation       | 271 µW                  | 219 µW   | Reduced by 19%       |  |  |

| Unity Gain<br>Frequency | 25 MHz                  | 22.6 MHz | Decreased by 2.4 MHz |  |  |

#### Table 3: Comparison between previous and proposed result.

Using 90 nm technology, after the simulation of 2 stage CMOS operational amplifier the results comes out on different parameters are much better than the previous results. As shown in table 3 the voltage gain margin is increased by 82%, phase margin is increased by 15%, power dissipation is reduced by 19% and unity gain frequency is decreased by 2.4MHz. Thus the operational amplifier stability is increased as phase margin increased, the gain is also increased and the power dissipation is reduced from previous result which makes the operational amplifier a stable, high gain and less power consumption amplifier.

#### 5. CONCLUSION

As integrated circuit systems are created to appear as single-pole systems over a wide frequency range to reduce the problem that second order systems encounter with regard to stability, the simulation was performed using Cadence tool with 90nm technology. In order to achieve some design specification requirements, such as voltage gain and a better phase margin, Miller compensation technique is used. The gain has been improved by adjusting the parameters up to 82 dB. The circuit is appropriate for high performance, low power VLSI applications. The gain

bandwidth product result comes to be 22.6228 MHz. The power dissipation is of 219  $\mu$ W and phase margin of 69° which makes the proposed operational amplifier suitable for low power operation with greater stability.

## REFERENCE

- [1] Boaz Shem-Tov, Mucahit Kozak, and Eby G. Friedman, "A High Speed CMOS Op-Amp Design Techniques using Negative Miller Capacitance," proceedings of the 11th IEEE International Conference on Electronics, circuit and systems, December 2004.

- [2] F Aziz, N Ahmad and F A S Musa, "90nm Two-Stage Operational Amplifier Using Floating-gate MOSFET", 4th Electronic and Green Materials International Conference 2018 (EGM 2018), December 2018, AIP Publishing. 978-0-7354-1771-7/\$30.00

- [3] Kanika Sharma, Rahil Kumar, "Design of a Two Stage CMOS operational amplifier using 180nm and 90nm technology", International Journal of Advanced Research in Electrical Electronics and Instrumentation Engineering, Vol. 5, Issue 5, May 2016.

- [4] Sumukh Nitundil, Nihal Singh, Rushabha Balaji, Pankaj Arora, "Design and Comparative analysis of a Two-Stage Ultra-Low-Power Subthreshold Operational Amplifier in 180nm, 90nm, and 45nm technology", 2021 Devices for Integrated Circuit (DevIC), 19-20 May 2021, DOI: 10.1109/DevIC50843.2021.9455791.

- [5] S. S. Rajput, A. Singh, A. K. Chandel, and R. Chandel, "Design of Low-Power High-Gain Operational Amplifier for Bio-Medical Applications," in 2016 IEEE Computer Society Annual Symposium on VLSI, 2016, pp. 355– 360.

- [6] K. A. Ng and Y. P. Xu, "A Low-Power, High CMRR Neural Amplifier System Employing CMOS Inverter-Based OTAs With CMFB Through Supply Rails," IEEE JOURNAL OF SOLID-STATE CIRCUITS, vol. 51, no. 3, pp. 724–737, 2016.

- [7] C. Yadav and S. Prasad, "Low Voltage Low Power Sub-threshold Operational Amplifier in 180nm CMOS," in 2017 Third international conference on sensing, signal processing and security (ICSSS), 2017, pp. 35–38.

- [8] J. Magri, I. Grech, O. Casha, E. Gatt, and J. Micallef, "Design of CMOS Front-End Circuitry for the Acquisition of Biopotential Signals," in 2016 IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2016, pp. 161–164.

- [9] K. N. Abhilash, S. Bose and A. Gupta, "A high gain, high CMRR two-stage fully differential amplifier using gm/Id technique for bio-medical applications," 2013 IEEE Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics (PrimeAsia), Visakhapatnam, India, 2013, pp. 40-45, doi: 10.1109/PrimeAsia.2013.6731175.

- [10] B. Razavi, "Design of Analog CMOS Integrated Circuits", New York: Mc-Graw Hill, 2001.

[11] D. Johns and Ken Martin, "Analog Integrated Circuit Design", Wiley India Pvt. Ltd, 1997.

- [12] Henil Langalia, Sarthak Lad, Mangesh Lolge and Surendra Rathod, "Analysis of two-stage CMOS Op-Amp for Single- Event Transients" International Conference on Communication, Information & Computing Technology (ICCICT), Oct. 19-20,2012, Mumbai, India, pp. 1-4.

- [13] Sunil M.P and Hari Krishna Murthy, "Design and Implementation of 90dB-4mW Two Stage CMOS Operational Amplifier Using 180nm" 3rd International Conference on Electronics and Communication Systems (ICECS-2016) 25-26th, February 2016, Coimbatore, Tamilnadu, India

- [14] C. L. Kavyashree, M. Hemambika, K. Dharani, A. V. Naik and M. P. Sunil, "Design and implementation of two stage CMOS operational amplifier using 90nm technology," 2017 International Conference on Inventive Systems and Control (ICISC), 2017, pp. 1-4, doi: 10.1109/ICISC.2017.8068601.

- [15] M. El-Sisi and M. Dessouky, "Procedural analog design automation using building block optimization," 2015 IEEE International Conference on Electronics, Circuits, and Systems (ICECS), 2015, pp. 474-477, doi: 10.1109/ICECS.2015.7440351.